C-DNN: Complementary Deep-Neural-Network Processor

본문

Overview

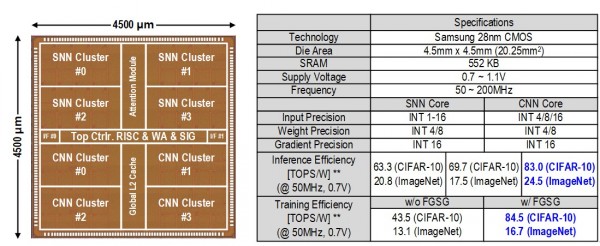

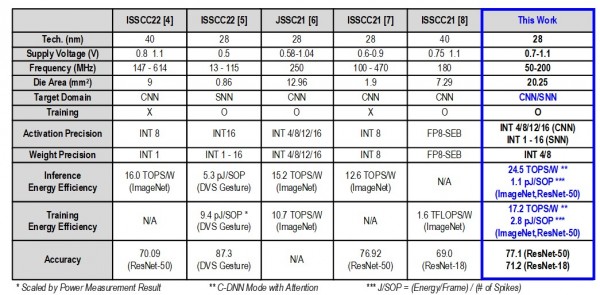

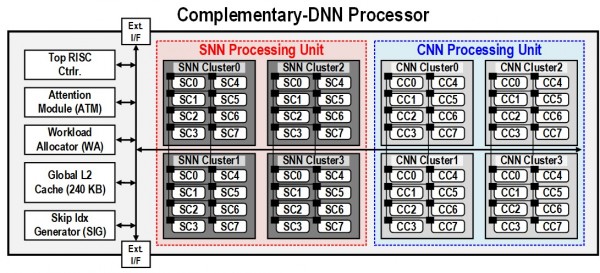

In this paper, we propose a Complementary-Deep-Neural-Network (C-DNN) processor by combining CNN and SNN to take advantage of them. The C-DNN processor can support both complementary inference and training with heterogenous CNN and SNN core architecture. In addition, the C-DNN processor is the first DNN accelerator AISC that can support CNN-SNN workload division by using their magnitude-energy trade-off. The proposed processor achieves an energy efficiency of 85.8 TOPS/W and 79.9 TOPS/W for inference with CIFAR-10 and CIFAR-100, respectively (VGG-16). Moreover, the C-DNN processor achieves ImageNet classification with state-of-the-art energy efficiency, of 24.5 TOPS/W (ResNet-50). For training, the C-DNN processor achieves the state-of-the-art energy efficiency of 84.5 TOPS/W and 16.7 TOPS/W for CIFAR-10 and ImageNet, respectively.

Features

- CNN-SNN workload division and attention module

- SNN PE array with Distributed L1 cache

- Forward gradient based sparsity generation and sparse CNN core

- Global counter and local gradient unit

Related Papers

- ISSCC 2023