DSPU: Low-power 3D Object Recognition Processor

본문

Overview

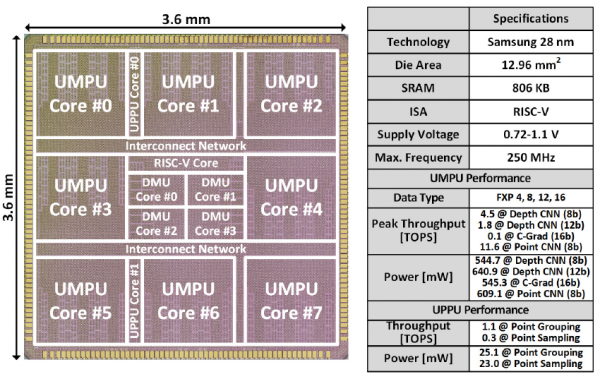

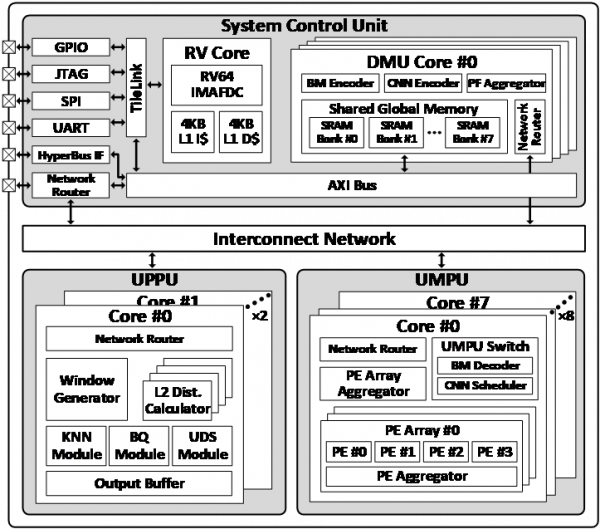

A low-latency and low-power dense RGB-D acquisition and 3D bounding-box extraction system-on-chip, DSPU, is proposed. The DSPU produces accurate dense RGB-D data through CNN-based monocular depth estimation and sensor fusion with a low-power ToF sensor. Furthermore, it performs a 3D point cloud-based neural network for 3D bounding-box extraction. The architecture of the DSPU accelerates the system by alleviating the data-intensive and computation-intensive operations. Finally, the DSPU achieves real-time implementation with 281.6 mW of end-to-end RGB-D and 3D bounding-box extraction.

Features

- A low power depth signal processing system

- Band matrix encoder and decoder

- Point feature reuse with pipelined architecture

- Shared unified point processing unit

Related Papers

- ISSCC 2022